Adakah anda tahu bagaimana untuk menyelesaikan masalah EMI apabila reka bentuk PCB berbilang lapisan?

Biar saya beritahu awak!

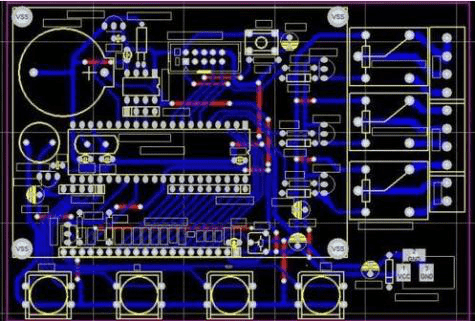

Terdapat banyak cara untuk menyelesaikan masalah EMI.Kaedah penindasan EMI moden termasuk: menggunakan salutan penindasan EMI, memilih bahagian penindasan EMI yang sesuai dan reka bentuk simulasi EMI.Berdasarkan susun atur PCB yang paling asas, kertas kerja ini membincangkan fungsi tindanan PCB dalam mengawal sinaran EMI dan kemahiran reka bentuk PCB.

bas kuasa

Lompatan voltan keluaran IC boleh dipercepatkan dengan meletakkan kapasitans yang sesuai berhampiran pin kuasa IC.Walau bagaimanapun, ini bukan penamat masalah.Oleh kerana tindak balas frekuensi terhad kapasitor, adalah mustahil untuk kapasitor menjana kuasa harmonik yang diperlukan untuk memacu keluaran IC dengan bersih dalam jalur frekuensi penuh.Selain itu, voltan sementara yang terbentuk pada bas kuasa akan menyebabkan penurunan voltan pada kedua-dua hujung kearuhan laluan penyahgandingan.Voltan sementara ini ialah sumber gangguan EMI mod biasa utama.Bagaimanakah kita boleh menyelesaikan masalah ini?

Dalam kes IC pada papan litar kami, lapisan kuasa di sekeliling IC boleh dianggap sebagai kapasitor frekuensi tinggi yang baik, yang boleh mengumpul tenaga yang dibocorkan oleh kapasitor diskret yang menyediakan tenaga frekuensi tinggi untuk output bersih.Di samping itu, induktansi lapisan kuasa yang baik adalah kecil, jadi isyarat sementara yang disintesis oleh induktor juga kecil, sekali gus mengurangkan mod biasa EMI.

Sudah tentu, sambungan antara lapisan bekalan kuasa dan pin bekalan kuasa IC mestilah sesingkat mungkin, kerana kelebihan isyarat digital yang semakin meningkat adalah lebih pantas dan pantas.Adalah lebih baik untuk menyambungkannya terus ke pad di mana pin kuasa IC terletak, yang perlu dibincangkan secara berasingan.

Untuk mengawal EMI mod biasa, lapisan kuasa mestilah sepasang lapisan kuasa yang direka bentuk dengan baik untuk membantu menyahgandingan dan mempunyai kearuhan yang cukup rendah.Mungkin ada yang bertanya, sejauh mana kebaikannya?Jawapannya bergantung pada lapisan kuasa, bahan antara lapisan, dan kekerapan operasi (iaitu, fungsi masa kenaikan IC).Secara amnya, jarak lapisan kuasa ialah 6mil, dan interlayer ialah bahan FR4, jadi kapasitansi setara bagi setiap inci persegi lapisan kuasa ialah kira-kira 75pF.Jelas sekali, semakin kecil jarak lapisan, semakin besar kapasitinya.

Tidak banyak peranti dengan masa kenaikan 100-300ps, tetapi mengikut kadar pembangunan semasa IC, peranti dengan masa naik dalam julat 100-300ps akan menduduki bahagian yang tinggi.Untuk litar dengan masa kenaikan 100 hingga 300 PS, jarak lapisan 3 juta tidak lagi digunakan untuk kebanyakan aplikasi.Pada masa itu, adalah perlu untuk mengguna pakai teknologi delaminasi dengan jarak interlayer kurang daripada 1mil, dan menggantikan bahan dielektrik FR4 dengan bahan dengan pemalar dielektrik tinggi.Kini, seramik dan plastik pasu boleh memenuhi keperluan reka bentuk litar masa kenaikan 100 hingga 300ps.

Walaupun bahan dan kaedah baharu boleh digunakan pada masa hadapan, litar masa kenaikan 1 hingga 3 ns biasa, jarak lapisan 3 hingga 6 mil, dan bahan dielektrik FR4 biasanya mencukupi untuk mengendalikan harmonik mewah dan membuat isyarat sementara cukup rendah, iaitu , mod biasa EMI boleh dikurangkan dengan sangat rendah.Dalam kertas ini, contoh reka bentuk susunan berlapis PCB diberikan, dan jarak lapisan diandaikan 3 hingga 6 mil.

perisai elektromagnet

Dari sudut pandangan penghalaan isyarat, strategi pelapisan yang baik adalah meletakkan semua jejak isyarat dalam satu atau lebih lapisan, yang berada di sebelah lapisan kuasa atau satah tanah.Untuk bekalan kuasa, strategi pelapisan yang baik ialah lapisan kuasa bersebelahan dengan satah tanah, dan jarak antara lapisan kuasa dan satah tanah hendaklah sekecil mungkin, iaitu apa yang kita panggil strategi "pelapis".

Timbunan PCB

Apakah jenis strategi susun yang boleh membantu melindungi dan menyekat EMI?Skim tindanan berlapis berikut mengandaikan bahawa arus bekalan kuasa mengalir pada satu lapisan dan voltan tunggal atau voltan berbilang diedarkan di bahagian berlainan lapisan yang sama.Kes berbilang lapisan kuasa akan dibincangkan kemudian.

pinggan 4 lapis

Terdapat beberapa masalah yang berpotensi dalam reka bentuk lamina 4 lapis.Pertama sekali, walaupun lapisan isyarat berada di lapisan luar dan kuasa dan satah tanah berada di lapisan dalam, jarak antara lapisan kuasa dan satah tanah masih terlalu besar.

Jika keperluan kos adalah yang pertama, dua alternatif berikut kepada papan 4 lapis tradisional boleh dipertimbangkan.Kedua-duanya boleh meningkatkan prestasi penindasan EMI, tetapi ia hanya sesuai untuk kes di mana ketumpatan komponen pada papan adalah cukup rendah dan terdapat kawasan yang mencukupi di sekeliling komponen (untuk meletakkan salutan tembaga yang diperlukan untuk bekalan kuasa).

Yang pertama ialah skim pilihan.Lapisan luar PCB adalah semua lapisan, dan dua lapisan tengah adalah lapisan isyarat / kuasa.Bekalan kuasa pada lapisan isyarat disalurkan dengan garis lebar, yang menjadikan impedans laluan arus bekalan kuasa rendah dan impedans laluan jalur mikro isyarat rendah.Dari perspektif kawalan EMI, ini adalah struktur PCB 4 lapisan terbaik yang tersedia.Dalam skema kedua, lapisan luar membawa kuasa dan tanah, dan dua lapisan tengah membawa isyarat.Berbanding dengan papan 4 lapisan tradisional, penambahbaikan skema ini adalah lebih kecil, dan impedans interlayer tidak sebaik papan 4 lapisan tradisional.

Jika galangan pendawaian hendak dikawal, skim susun di atas hendaklah berhati-hati untuk meletakkan pendawaian di bawah pulau tembaga bekalan kuasa dan pembumian.Di samping itu, pulau tembaga pada bekalan kuasa atau lapisan harus saling bersambung sebanyak mungkin untuk memastikan ketersambungan antara DC dan frekuensi rendah.

pinggan 6 lapis

Jika ketumpatan komponen pada papan 4 lapisan adalah besar, plat 6 lapisan adalah lebih baik.Walau bagaimanapun, kesan perisai beberapa skema susun dalam reka bentuk papan 6 lapisan tidak cukup baik, dan isyarat sementara bas kuasa tidak berkurangan.Dua contoh dibincangkan di bawah.

Dalam kes pertama, bekalan kuasa dan pembumian masing-masing diletakkan di lapisan kedua dan kelima.Oleh kerana impedans tinggi bekalan kuasa berpakaian tembaga, adalah sangat tidak baik untuk mengawal sinaran EMI mod biasa.Walau bagaimanapun, dari sudut pandangan kawalan impedans isyarat, kaedah ini sangat betul.

Dalam contoh kedua, bekalan kuasa dan pembumian masing-masing diletakkan pada lapisan ketiga dan keempat.Reka bentuk ini menyelesaikan masalah impedans bersalut tembaga bekalan kuasa.Disebabkan oleh prestasi perisai elektromagnet yang lemah pada lapisan 1 dan lapisan 6, mod pembezaan EMI meningkat.Jika bilangan garis isyarat pada dua lapisan luar adalah paling sedikit dan panjang garisan adalah sangat pendek (kurang daripada 1 / 20 panjang gelombang harmonik tertinggi isyarat), reka bentuk boleh menyelesaikan masalah mod pembezaan EMI.Keputusan menunjukkan bahawa penindasan mod pembezaan EMI amat baik apabila lapisan luar diisi dengan kuprum dan kawasan bersalut kuprum dibumikan (setiap 1 / 20 selang panjang gelombang).Seperti yang dinyatakan di atas, tembaga hendaklah diletakkan

Masa siaran: Jul-29-2020